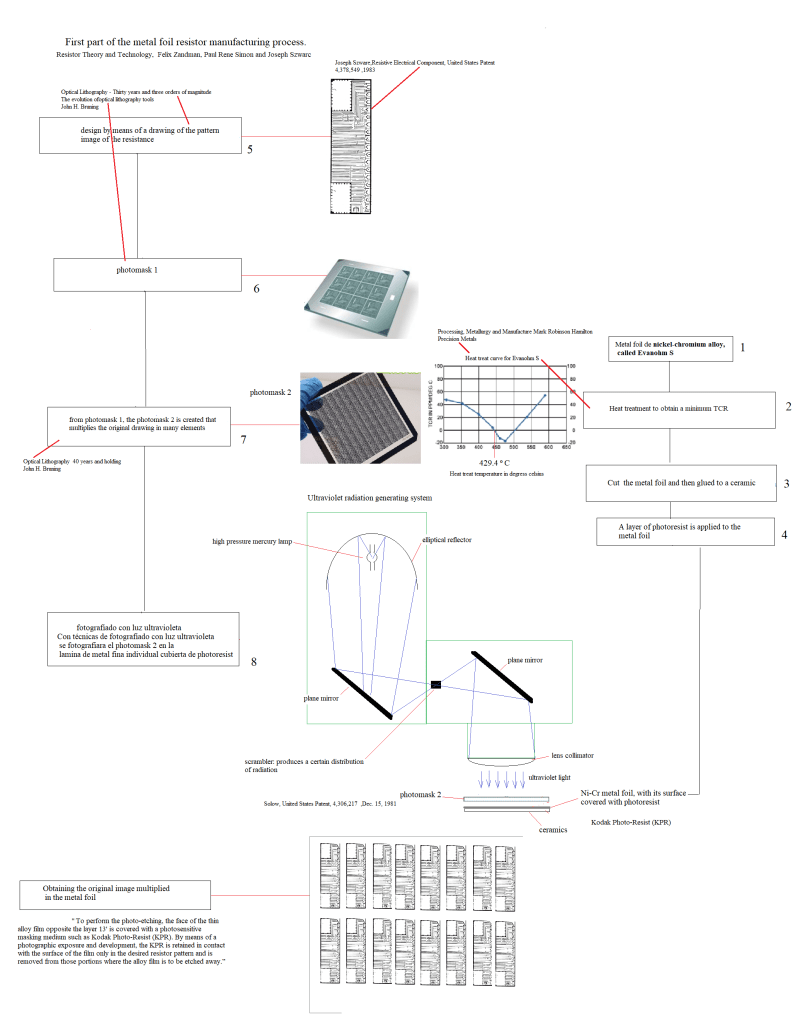

La siguiente ilustracion refleja la la primera parte del proceso de fabricacion del metal foil resistor, con las fuentes bibliograficas adjuntas.

Ver Resistencias de lamina fina, metal foil resistors. Charly Garcia

https://sites.google.com/view/metal-foil-resistor/

Más de cincuenta años después de su invención por el físico Dr. Felix Zandman en 1962, la tecnología Bulk Metal Foil aún supera a todas las demás tecnologías de resistencias disponibles en la actualidad para aplicaciones que requieren precisión, estabilidad y confiabilidad. Estos productos VFR Bulk Metal Foil se ofrecen en una variedad de configuraciones de resistencias y tipos de paquetes para satisfacer las necesidades de una amplia gama de aplicaciones, ofrecen un coeficiente de temperatura absoluto de resistencia (TCR) de ±0,2 ppm/°C (–55 °C a +125 °C, +25 °C ref.), un orden de magnitud mejor que las tecnologías de láminas anteriores. Cuanto más bajo es el TCR absoluto, mejor puede una resistencia mantener su valor preciso a pesar de las variaciones de temperatura ambiente y el autocalentamiento cuando se aplica energía. Una aleación de lámina específica con propiedades conocidas y controlables (Ni/Cr con aditivos) se cementa a un sustrato cerámico, lo que da como resultado un equilibrio termomecánico de fuerzas. A continuación, se fotograba un patrón resistivo en la lámina. Este proceso combina de manera única las características importantes de bajo TCR, estabilidad a largo plazo, no inductancia, baja capacitancia, rápida estabilización térmica y bajo nivel de ruido en una sola tecnología de resistencia. Estas capacidades brindan alta estabilidad y confiabilidad al rendimiento del sistema sin comprometer la precisión, la estabilidad y la velocidad. Para adquirir un valor de resistencia de precisión, el chip Metal Foil se recorta eliminando selectivamente las «barras de cortocircuito» incorporadas. Para aumentar la resistencia en incrementos conocidos, se cortan áreas seleccionadas, lo que produce aumentos de resistencia progresivamente menores. En la lámina plana, el diseño de elementos con un patrón paralelo reduce la inductancia; la inductancia total máxima de la resistencia es de 0,08 μH. La capacitancia es de 0,5 pF como máximo. Una resistencia de 1 kΩ tiene un tiempo de establecimiento de menos de 1 ns hasta 100 MHz. El tiempo de subida depende del valor de la resistencia, pero los valores más altos y más bajos son solo un poco más lentos que los valores de rango medio. La ausencia de timbre es especialmente importante en la conmutación de alta velocidad como, por ejemplo, en la conversión de señales. La resistencia de CC de una resistencia de lámina metálica a granel de 1 kΩ en comparación con su resistencia de CA a 100 MHz se puede expresar de la siguiente manera: resistencia de CA/resistencia de CC = 1,001. Las técnicas de lámina producen una combinación de especificaciones de resistencias altamente deseables y previamente inalcanzables. Al aprovechar la estabilidad y confiabilidad general de las resistencias, los diseñadores pueden reducir significativamente los errores del circuito y mejorar en gran medida el rendimiento general del circuito.

Resistor Theory and Technology, Felix Zandman, Paul Rene Simon and Joseph Szwarc, 2001.